The GX3500 provides 160 I/O Channels that can be connected to the front connectors or the optional expansion daughter board, in groups of 40. To connect the I/O channels to the daughter board, the user disconnect jumpers, JP3 to JP6 for the Bi-Directional Level Shifting Switches, this routs the I/O channels to the daughter board. If the user does not use the optional daughter board and wants to connect the I/O channels directly to the front panel connectors then enabling the Bi-Directional Level Shifting Switches by connecting jumpers JP3, JP4, JP5 and JP6 will route the I/O signals from the user FPGA to the front panel connectors. When connected, each one of these jumpers will permanently select and enable 40 I/O channels to be routed directly to the front panel connectors. For more information see table GX3500 Connectors and Jumpers and the section Expansion Boards.

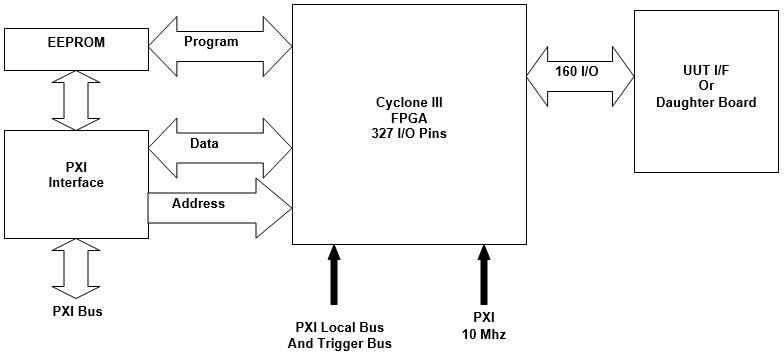

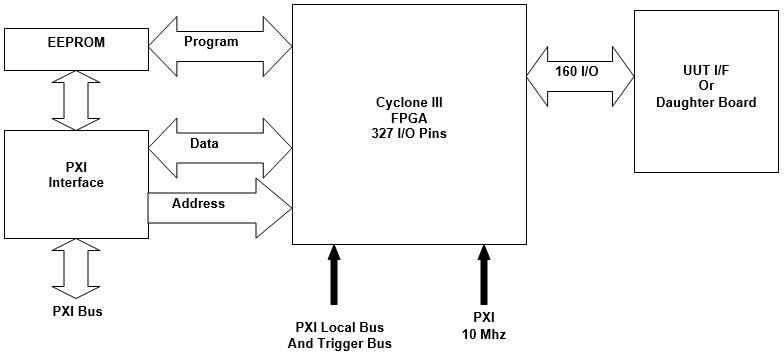

The User FPGA, a Cyclone III, can be configured either through the EEPROM or directly through the PXI Interface. The User FPGA has access to PXI resources such as the local bus, trigger bus, and PXI 10 MHz clock source. The User FPGA is connected to the PXI Interface FPGA to give access to PCI resources and memory. This allows the User FPGA to communicate with the host system’s operating system by utilizing the provided GXFPGA software driver.